UNIVERSITÉ CATHOLIQUE DE LOUVAIN ECOLE POLYTECHNIQUE DE LOUVAIN ICTEAM INSTITUTE

# Towards the design of a pseudo-synchronous multi-processor system-on-chip for processing-intensive ultra-low-power applications

# François Botman

Thesis submitted in partial fulfillment of the requirements for the degree of *Docteur en sciences appliquées*

Dissertation committee: Prof. Jean-Didier Legat (UCLouvain, Belgium), Advisor, Prof. David Bol (UCLouvain, Belgium), Advisor, Prof. Denis Flandre (UCLouvain, Belgium), President, Prof. François-Xavier Standaert (UCLouvain, Belgium), Prof. Marc Belleville (CEA-LETI, France), Prof. Andreas Burg (EPFL, Switzerland).

September 2014

# CONTENTS

| Acknow | wledgm              | ents                                        | vii        |

|--------|---------------------|---------------------------------------------|------------|

| Abstra | $\operatorname{ct}$ |                                             | ix         |

| Acrony | 7ms                 |                                             | xi         |

| Introd | uction              |                                             | xv         |

| I.1    | Struc               | ture of a Wireless Sensor Node              | XV         |

| I.2    | The                 | IoT vision                                  | xvii       |

| I.3    | Purp                | ose of this Thesis                          | xvii       |

| I.4    | Thes                | is outline                                  | xviii      |

| Author | s publ              | ication list                                | xxi        |

| 1 Fur  | ndamen              | tals of low-power processor design          | 1          |

| 1.1    | Circu               | it design for ultra-low power               | 3          |

| 1.2    | ULV                 | circuit implementation challenges           | 9          |

| 1.3    | Micro               | o-controller design metrics                 | 13         |

| 1.4    | A bri               | ief background on energy harvesting systems | 14         |

| 1.5    | Micro               | o-controllers for ultra-low power systems   | 15         |

| 1.6    | Next                | steps                                       | 18         |

| 2 Bel  | levue:              | a low-power micro-controller for processing | -intensive |

| арр    | olication           | IS                                          | 21         |

| 2.1    | Belle               | vue system architecture                     | 23         |

| 2.2    | Proc                | essor design                                | 24         |

|        | 2.2.1               | Choice of architecture                      | 24         |

|        | 2.2.2               | Switching isolation and glitch reduction    | 25         |

|        | 2.2.3               | Variable-width SIMD pipeline                | 26         |

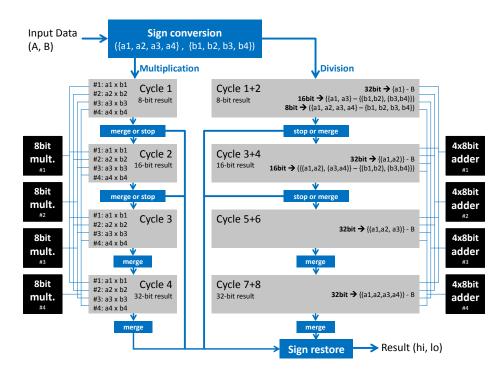

|        | 2.2.4               | Multiply-Divide (MAD) Unit                  | 27         |

|        | 2.2.5               | Dedicated compiler                          | 29         |

|        | 2.2.6               | Summary of features                         | 29         |

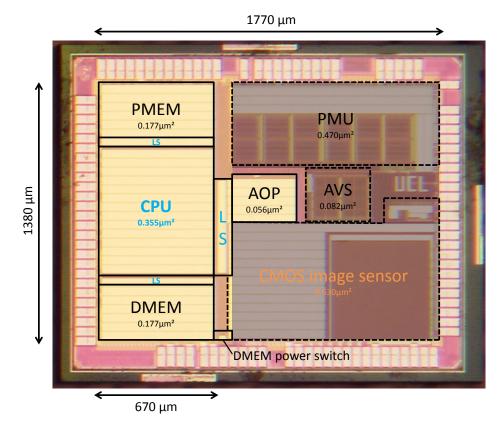

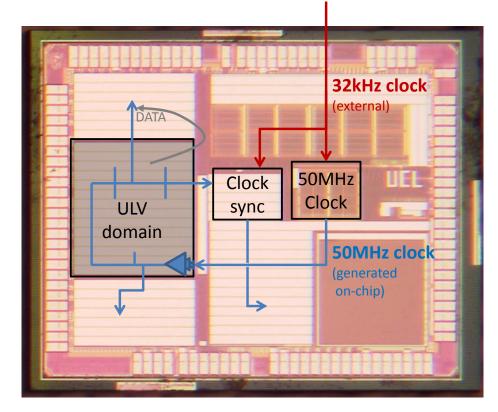

| 2.3    | Phys                | ical implementation                         | 30         |

|        |                     |                                             | iii        |

# iv contents

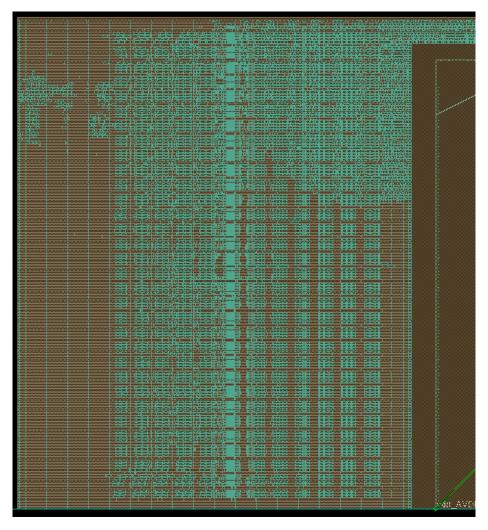

|     | 2.3.1 | SoC implementation flow                | 30 |

|-----|-------|----------------------------------------|----|

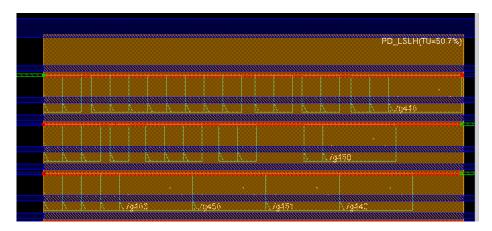

|     | 2.3.2 | Level-shifter cell alignment challenge | 33 |

|     | 2.3.3 | Light protection                       | 34 |

|     | 2.3.4 | CIS routing congestion challenge       | 34 |

|     | 2.3.5 | Implementation summary                 | 36 |

| 2.4 | Resul | ts                                     | 37 |

|     | 2.4.1 | Image sharpening application           | 38 |

|     | 2.4.2 | Comparison to other systems            | 40 |

|     | 2.4.3 | Comparison to sensor-only systems      | 41 |

| 2.5 | Concl | usion                                  | 43 |

| 3 | Pseu | udo-syn | chronicity:     | an     | orthogonal | data-dependant | operation |    |

|---|------|---------|-----------------|--------|------------|----------------|-----------|----|

|   | spee | edup te | chnique         |        |            |                |           | 47 |

|   | 3.1  | Prope   | sed technique   |        |            |                |           | 49 |

|   | 3.2  | Dedic   | ated cells      |        |            |                |           | 52 |

|   |      | 3.2.1   | Dedicated T     | D ce   | 211        |                |           | 52 |

|   |      | 3.2.2   | Large-input     | OR     | cells      |                |           | 53 |

|   | 3.3  | Imple   | mentation and   | l Re   | sults      |                |           | 56 |

|   |      | 3.3.1   | Implementat     | ion    |            |                |           | 56 |

|   |      | 3.3.2   | Testbench ci    | rcuit  | ts         |                |           | 58 |

|   |      | 3.3.3   | Simulation r    | esult  | s          |                |           | 59 |

|   | 3.4  | Optin   | nized synthesis | s flov | N          |                |           | 65 |

|   | 3.5  | Concl   | usion           |        |            |                |           | 72 |

# 4 Ianus: a dual-processor approach to the WSN workload balancing problem 75

| Propo     | sed technique                                                                           | 78                                                                                                                                                                                                                                                    |

|-----------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Imple     | mentation                                                                               | 79                                                                                                                                                                                                                                                    |

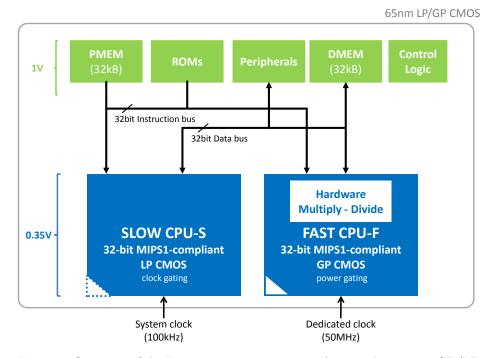

| 4.2.1     | System architecture                                                                     | 79                                                                                                                                                                                                                                                    |

| 4.2.2     | Processor cores                                                                         | 81                                                                                                                                                                                                                                                    |

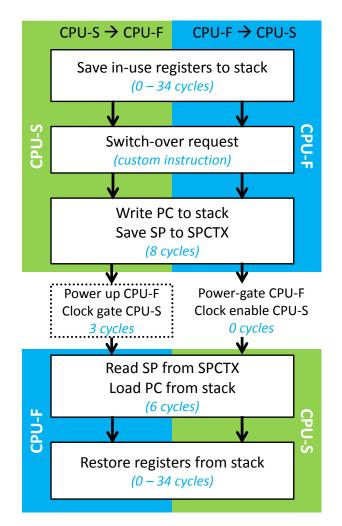

| 4.2.3     | Switch-over mechanism                                                                   | 82                                                                                                                                                                                                                                                    |

| 8 Results |                                                                                         | 84                                                                                                                                                                                                                                                    |

| 4.3.1     | Benchmark programs                                                                      | 84                                                                                                                                                                                                                                                    |

| 4.3.2     | Test conditions                                                                         | 85                                                                                                                                                                                                                                                    |

| 4.3.3     | Power estimation procedure                                                              | 85                                                                                                                                                                                                                                                    |

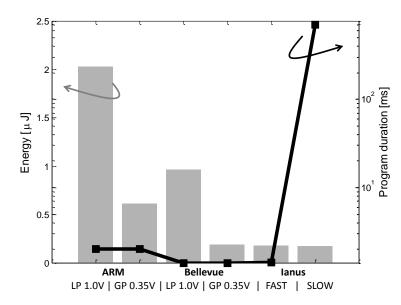

| 4.3.4     | Core performance comparison                                                             | 86                                                                                                                                                                                                                                                    |

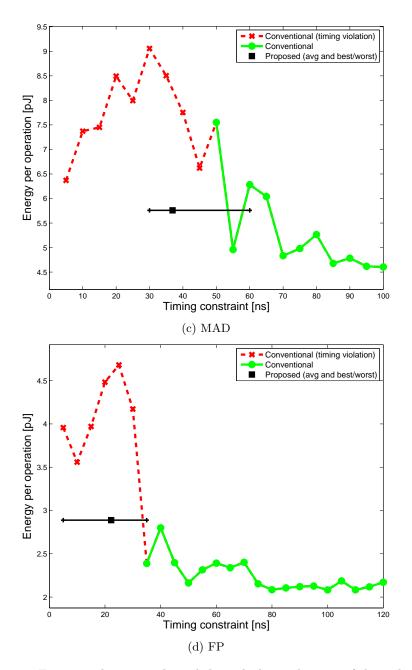

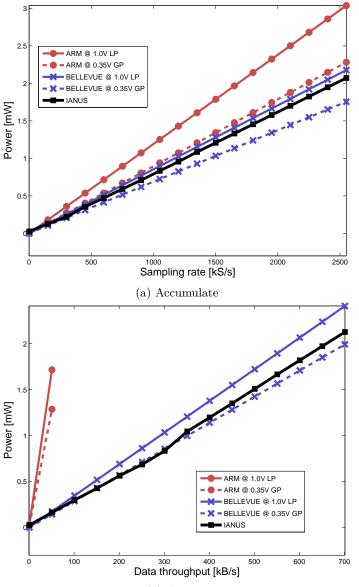

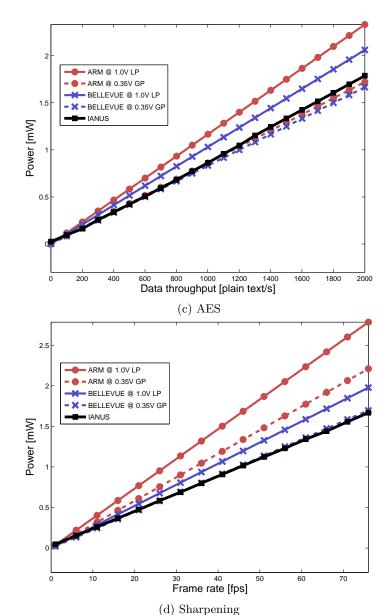

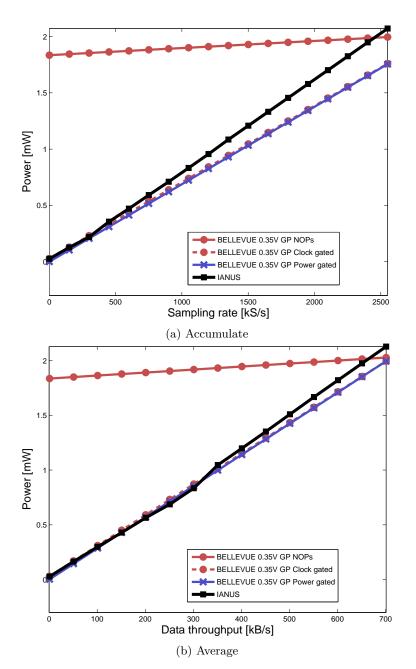

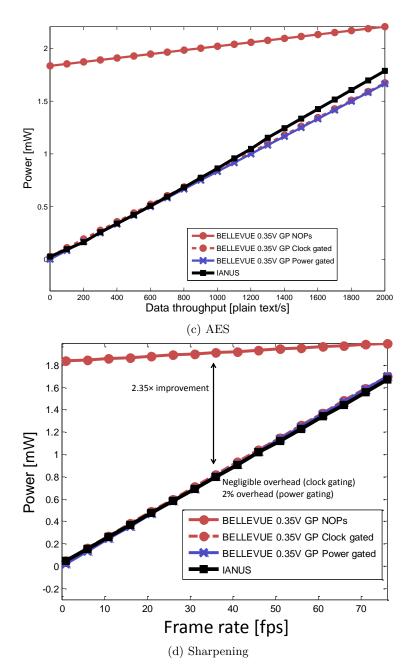

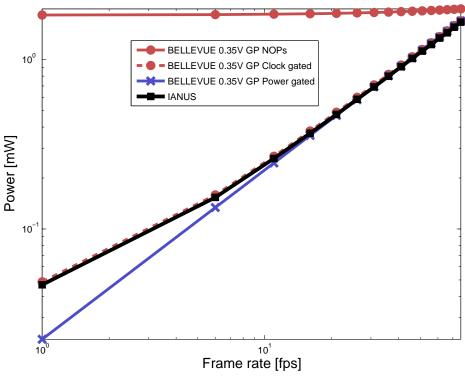

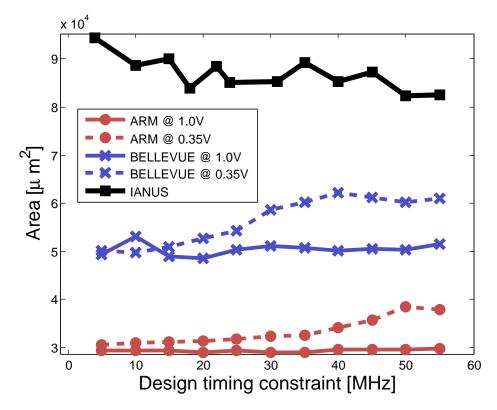

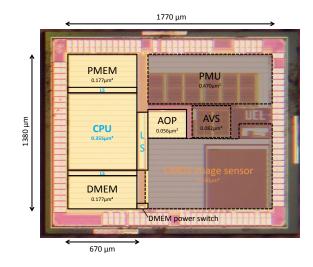

| 4.3.5     | Workload-dependent performance achieved                                                 | 88                                                                                                                                                                                                                                                    |

| Concl     | usion                                                                                   | 95                                                                                                                                                                                                                                                    |

|           | Imple<br>4.2.1<br>4.2.2<br>4.2.3<br>Result<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5 | <ul> <li>4.2.2 Processor cores</li> <li>4.2.3 Switch-over mechanism</li> <li>Results</li> <li>4.3.1 Benchmark programs</li> <li>4.3.2 Test conditions</li> <li>4.3.3 Power estimation procedure</li> <li>4.3.4 Core performance comparison</li> </ul> |

|                              | CONTENTS | v   |

|------------------------------|----------|-----|

| Conclusions and perspectives |          | 97  |

| References                   |          | 105 |

# ACKNOWLEDGMENTS

A thesis is not only the culmination of years of research resulting in an advancement of the state-of-the-art for a given field; it is also a personal journey leading to the mastery of the chosen field and the attainment of the scientific culture and rigour that such an undertaking requires. Such a journey is not a lone voyage, for it is the meetings and interactions with extraordinary people that enrich it and make it of relevance. Looking back along the road I have travelled, I see how much I have learnt and am truly grateful to those who helped, stimulated, challenged and encouraged me along the way.

In particular, I would like to thank my advisor, Pr. Jean-Didier Legat, for both encouraging me to undertake this challenge, for giving me incredible resources and freedom with which to pursue it, and for his unwavering confidence and support throughout.

I would also like to thank Pr. David Bol, who initiated the chip design projects I had the opportunity of working on that gave me invaluable experience in the tape-out process and technological aspects, and whose support, insight, and challenges have forced me to become, I hope, a better scientist.

I am also grateful to Pr. Kaushik Roy, with whom I worked at Purdue during the autumn of 2012. I have often had cause to profoundly respect his wisdom and insight, and working together truly widened my horizons. The time I spent at Purdue will forever remain a cherished memory.

I would also like to thank the distinguished members of my jury, Pr. Marc Belleville, Pr. Andreas Burg, Pr. Denis Flandre, and Pr. François-Xavier Standaert for their encouragement, valuable feedback, and all their work associated with this thesis.

I am also grateful to the CETIC, Walloon region of Belgium and the European fund for regional developments for funding this work.

Lastly, I would like to thank my family, friends and colleagues for the encouragements, the horizon-broadening discussions, and for all the fantastic moments we shared. Angelo Kuti, Julien De Vos, Guerric de Streel, Sébastien Bernard, and François Stas, the office would not have been the same without you. Adeline Decuyper, Emilie Renard, Maguy Trefois, Nicolas Boumal and Romain Hollanders, who have allowed me to glimpse at the mathematical beauty of the world, and Pierre-Antoine Haddad, Aline Emplit, Cédric Verleysen, Thomas Wallewyns and so many others for all the amazing times. And thank you to the administrative team, Viviane Sauvage, Anne Adant, Isabelle Dargent and Brigitte Dupont for their valuable help.

François.

# ABSTRACT

In the context of the Internet-of-Things (IoT), the number of Wireless Sensor Nodes (WSNs) is set to explode. Limited in their autonomy by the energy they can store or harvest, these nodes must ideally consume as little power as possible in order to maximize their lifespans. Since the sensor and wireless link are the largest energy drains, a good system-level optimization strategy is to include a processor to filter the data and intelligently manage the node, keeping it in sleep as long as practicable.

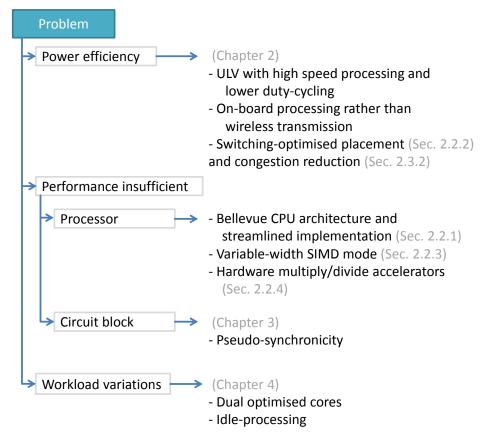

The design of such a processor is the research topic of this thesis, with a focus on performance and low power consumption since the overhead of such a processor in the system must be small. In particular, the following questions were asked;

- Can a processor provide sufficient computing performance to carry out high-level tasks and signal processing, specifically the on-board analysis of sensed image data, whilst operating within the constraints of an energy-harvesting system?

- Beyond traditional low-power design techniques, are there alternative circuit design strategies that could yield increased processing speed in low-power systems?

- How can processors be made to operate efficiently in spite of the varying workloads typical of such devices?

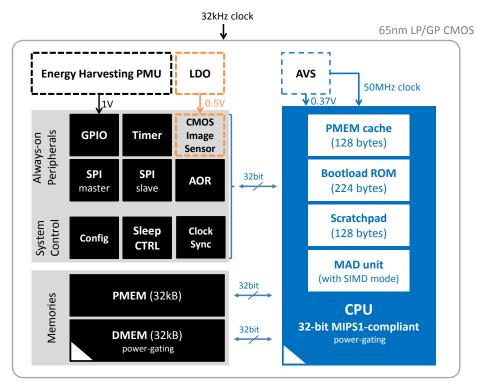

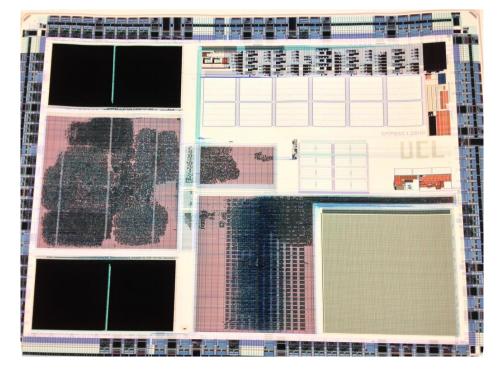

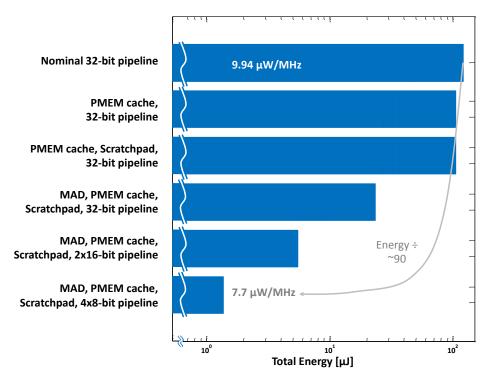

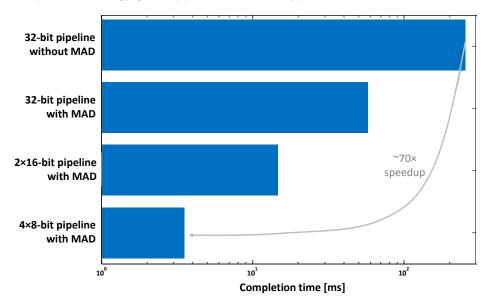

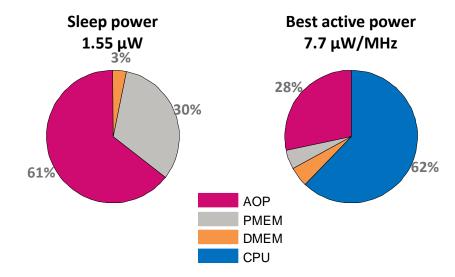

This thesis aims to answer these questions through three distinct contributions. Firstly, a custom-designed MIPS-1 instruction set compliant 5-stage pipelined 32-bit CPU was designed and, along with the top-level assembly of the associated System-on-Chip (SoC), taped-out. It is able to achieve over 50MHz operation at 0.37V, and is notable for its use of a dedicated multiply and divide (MAD) unit that operates in parallel with the main execution branch, and its introduction of a software-controlled variable-width pipeline throughout. This enables the processor to handle either complex 32-bit data, or operate in SIMD mode on  $2\times16$ -bit or  $4\times8$ -bit data. Interaction with an 8-bit sensor peripheral thus provides significant performance improvements. Overall, the processor achieves  $7.7\mu$ W/MHz operation at 50MHz, with a  $1.55\mu$ W sleep mode, thereby improving on state-of-the-art designs.

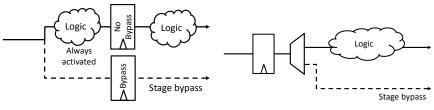

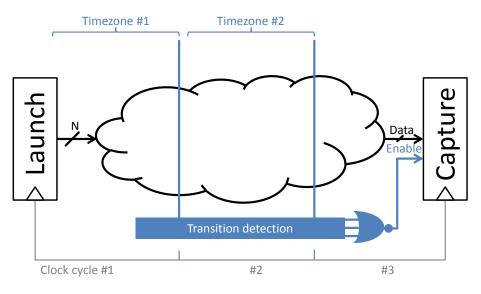

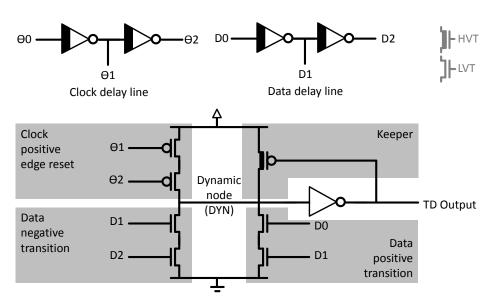

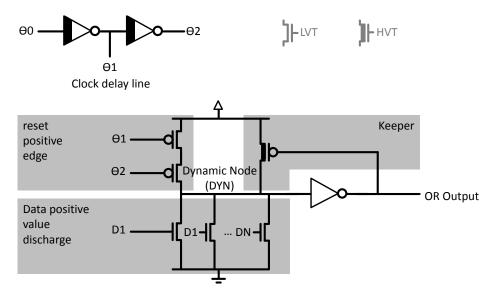

With this chip it became clear that good design practices and careful attention to low-power issues could result in a very economical processor. However, additional improvements are required in order to achieve performance beyond that and the benefits provided by technology scaling. This thesis therefore introduces pseudo-synchronicity, an orthogonal circuit-level optimization technique

# **X** ABSTRACT

that allows the acceleration of combinatorial circuits beyond the performance generally achievable by conventional synthesis and timing closure, by exploiting the data-dependent delay variations inherent in such circuits. Through the automatic insertion of transition detectors within the target circuit, the progress of operations underway can be monitored and prematurely completed, thereby increasing the operation speed from the worst towards the average case. In addition, a synthesis flow is proposed to increase the proportion of fast paths, thereby increasing the technique's impact. Applied automatically to a series of benchmark circuits, synthesis results show it to achieve an average performance increase of 29% over conventional synthesis, which must ensure deterministic timing closure. In spite of a power 21% overhead caused by the addition of the hardware required, this increased speed allows shorter wake periods and is thus able to lower the circuit's overall active energy by 14%.

Lastly, this thesis observed traditional workloads for WSNs and noted that in addition to bursts of high performance, for which the traditional sleep-wake model of processors was well suited, they also often needed continuous operation for monitoring tasks, for which current designs are badly suited. A dual-processor system is therefore presented that is able to operate efficiently in either highperformance burst or continuous monitoring modes. Software running onboard can transparently switch to a workload-optimized core during execution in order to best match the application and tasks being processed. In doing so it can either provide a lower-power performance for time-indifferent tasks, and provide flexible continuous monitoring capabilities during idle periods between processing bursts, or a DSP-capable core for data intensive tasks.

# ACRONYMS

| AES    | Advanced Encryption Standard            |

|--------|-----------------------------------------|

| ADC    | Analog to Digital Converter             |

| AOP    | Always-On Peripheral                    |

| AOR    | Always-On Register                      |

| AFS    | Adaptive Frequency Scaling              |

| AVS    | Adaptive Voltage Scaling                |

| BAN    | Body-Area Network                       |

| BL     | BootLoader                              |

| BPS    | Bits Per Second                         |

| CAD    | Computer-Aided Design tools             |

| CIS    | CMOS Imaging System                     |

| CISC   | Complex Instruction Set Computer        |

| CMOS   | Complementary Metal-Oxide Semiconductor |

| COTS   | Commercial, Off-The-Shelf               |

| CPF    | Cadence Power Format                    |

| CPR    | Critical-Path Replica                   |

| CPU    | Central Processing Unit                 |

| CRC    | Cyclic Redundancy Check                 |

| CT     | Clock Tree                              |

| D\$    | Data Cache                              |

| D2D    | Die-to-Die variations                   |

| DIBL   | Drain-Induced Barrier Lowering          |

| DMEM   | Data MEMory                             |

| DMA    | Direct Memory Access                    |

| DSP    | Digital Signal Processing               |

| DVFS   | Dynamic Voltage and Frequency Scaling   |

| EOV    | Energy-Optimal Voltage                  |

| FD-SOI | Fully Depleted Silicon-On-Insulator     |

|        |                                         |

# xii ACRONYMS

| $\mathbf{FF}$ | Flip-Flop                                              |

|---------------|--------------------------------------------------------|

| FFT           | Fast Fourier Transform                                 |

| FIFO          | First-In, First-Out (a memory buffer interface system) |

| FIR           | Finite Impulse Response filter                         |

| GPIO          | General-Purpose Input Output                           |

| HDL           | Hardware Description Language, eg: Verilog, VHDL       |

| HDR           | High Dynamic Range                                     |

| I\$           | Instruction Cache                                      |

| IC            | Integrated Circuit                                     |

| IMEM          | Instruction MEMory, as as PMEM                         |

| IoT           | Internet-of-Things                                     |

| IRQ           | Interrupt (request)                                    |

| JTAG          | Joint Test Action Group (a debugging and               |

|               | programming interface)                                 |

| LER           | Line Edge Roughness                                    |

| LDO           | Low Drop-Out (regulator)                               |

| LS            | Level Shifter                                          |

| LZR           | Line Width Roughness                                   |

| MAD           | Multiply and Divide (Unit)                             |

| MC            | Monte-Carlo simulation                                 |

| MEP           | Minimum Energy Point                                   |

| MEMS          | Micro Electro-Mechanical Systems                       |

| MMMC          | Multi-Mode, Multi-Corner                               |

| MOS           | Metal-Oxide Semiconductor                              |

| MOSFET        | Metal-Oxide Semiconductor Field Effect Transistor      |

| PCB           | Printed Circuit Board                                  |

| PMEM          | Program MEMory, same as IMEM                           |

| PMU           | Power Management Unit                                  |

| POR           | Power On Reset                                         |

| PVT           | Process, Voltage and Temperature                       |

| PWM           | Pulse Width Modulation                                 |

| RC            | Resistor-Capacitor                                     |

| RDF           | Random Dopant Fluctuations                             |

| $\mathbf{RF}$ | Radio-Frequency                                        |

|               |                                                        |

| RFID | Radio-Frequency IDentification                         |

|------|--------------------------------------------------------|

| RISC | Reduced Instruction Set Computer                       |

| RO   | Ring Oscillator                                        |

| ROM  | Read-Only memory                                       |

| RTL  | Register Transfer Level                                |

| SDC  | Synopsys Design Contraints                             |

| SDP  | Structured DataPath                                    |

| SFR  | Special Function Registers                             |

| SIMD | Single-Instruction, Multiple-Data                      |

| SoC  | System-on-Chip                                         |

| SOI  | Silicon-On-Insulator                                   |

| SPI  | Serial Peripheral Interface (a communication protocol) |

| SSTA | Statistical Static Timing Analysis                     |

| TD   | Transition Detector                                    |

| TDC  | Time-to-Digital Converter                              |

| TSV  | Through-Silicon Vias                                   |

| UART | Universal Asynchronous Receiver Transmitter (a         |

|      | communication protocol)                                |

| ULP  | Ultra-Low-Power                                        |

| ULV  | Ultra-Low-Voltage                                      |

| VLIW | Very Long Instruction Word                             |

| WDT  | Watchdog Timer                                         |

| WID  | WIthin-Die variations                                  |

| WSN  | Wireless Sensor Node                                   |

# INTRODUCTION

Fifty years ago, mankind witnessed something incredible: the landing of a man on the moon marked one of the greatest achievements of science and technology. Incredible perseverance, the will to solve all problems one by one was key to making the voyage possible. Among the many technological innovations of the Apollo program, perhaps one of the most significant was the Guidance and Navigation computer due to its small size, being one of the very earliest computers to be built using integrated circuits. Fifty years on, computers are both far more powerful and more integrated, with even the simplest pocket calculator able to outperform the Apollo computer, a fitting testimony to the pioneering spirit and engineering determination that inspired the original.

Enabling this incredible evolution of computers is the scaling of features capable of being integrated onto a silicon chip in a trend known as Moore's Law [1], allowing ever more functionality for ever-decreasing cost and size. In recent years, however, there has also been a diversification in end-use of the chips produced, moving away from high-power, high-performance devices such as desktop computers and servers to distributed, miniature, low-power wireless sensor networks. This trend is set to become increasingly important with the advent of a vision known as the Internet-of-Things (IoT), where data is to be accumulated from more sources and interact more intensely to enable new high-level, intelligent applications.

Enabling the IoT, and indeed vital for its operation, is the underlying array of Wireless Sensor Nodes (WSNs).

# I.1 STRUCTURE OF A WIRELESS SENSOR NODE

A wireless sensor node is an embedded system that sends sensor data to a control node over a wireless link, or receives instructions to perform some sort of actuation. For the IoT vision, where these WSNs are to be deployed ubiquitously and in large numbers, these must be small, standalone, and easy to maintain.

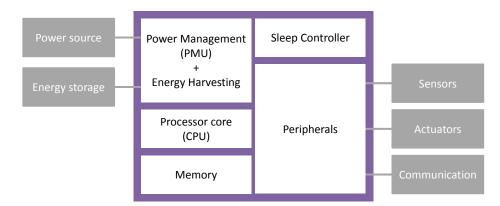

Figure I.1 shows the general structure of a typical WSN. Being sizeconstrained, the on-chip component integration is generally maximized, using external components only where necessary. The power source is dictated by the environment into which the sensor node is placed, but will often be of limited magnitude; in order to maximize autonomy and limit maintenance, such as the replacement of batteries, the system must be designed to function for as long as possible off a battery, or even directly employ energy available in the environment through energy harvesting methods [2]. It is therefore the role of the on-board Power Management Unit (PMU) to maximise the power that can be obtained xvi INTRODUCTION

Fig. I.1.: Typical architecture of a Wireless Sensor Node, showing the on-chip components (blue), and external interfaces (grey).

from the source, and manage any external reserves available, traditionally a small battery or even simply a large capacitor.

Also integrated externally are the sensors and actuators, and a communication interface such as a radio link to interact with nearby nodes and report back to a controller. These represent the useful payload of the sensor node, gathering and sending the raw data, but also represent the most power-intensive resources. Indeed, without pre-processing, it is very difficult to reduce the operating power down to manageable levels.

Several research directions are therefore possible to make these devices a reality; either the energy harvesting aspect needs to be improved in order to provide sufficient energy to power everything for the device lifespan, or the sensors and radios must be optimized to consume less. While these optimizations are significant, most WSNs also employ a system-level optimization, whereby the data is pre-processed on-chip before transmission. By adding a processor core, the node itself will have a power overhead, but in doing so the power-hungry components can be intelligently managed and on-board digital signal processing (DSP) can be used to minimize their active time, thereby bringing a significant power reduction to the overall system.

Having on-board processing capabilities also enables high-level functionality, such as the ability to manage a complex wireless network and prevent conflicts with other nodes, and features such as data security. It can also enable entropy coding, compressed sensing [3, 4], feature extraction and classification [5], or event detection, further reducing the amount of data that needs to be transmitted.

However, for this to be optimal, maximising a processor's signal processing and control functionalities with respect to power consumption becomes a priority. Optimizing the processor core for this case is the focus of this work.

# **I.2 THE IOT VISION**

It may be asked why any of this is necessary, what benefits such a technological investment can bring. After all, we already live in a technologically advanced society that is feeling the pressures of information overload, and adding more data sources seems redundant if not foolhardy. The IoT, more than simply an expansion of existing technology, is a paradigm shift in the way such technology is used. Even in the early days of computing, researchers at the famed Xerox PARC realised that users of technology were being forced to interact with it through very limited channels, such as screens and keyboards, in contrast to how they interacted with everyday objects [6]. If anything, this has become even more relevant in the modern day. Instead of interacting with technology through limited screens and keyboards, the IoT aims to interact with the human environment directly. The aim of the IoT is therefore to bring technology into the human environment, rather than forcing humans into the technological environment.

Another facet of the IoT is the strange realization that in fact more data is needed to provide meaningful information in large-scale systems. Whereas previously the main limitation was computational capabilities of dealing with the data, there exists today the ability and the necessity of dealing with more data in order to refine the underlying models and improve analysis and predictions. Through more advanced sensing techniques or vast arrays of sensors, the IoT vision aims to improve human lives by collecting and cross-correlating more data sources to form a more reliable and informative outcome.

This vision is also relevant at the individual level, where a myriad of sensors and networks seamlessly and transparently gather, analyse and transmit information to and from the user. Be they a short-range Body-Area Network (BAN), allowing different sensors embedded directly into a user's body to interact and communicate with the controllers in the home [7]. Or the home automation systems currently being considered, which must centralize information from a myriad of sources, such as RFID tags [8] in closets and sensors on the doors and windows, and compile them into relevant facts. Or a city-scale network that coordinates traffic, or even large-area networks [9] composed of randomly-positioned (air-dropped, for example) sensors for applications such as detecting forest fires before they are too large to contain. By cross-referencing all this information, by allowing devices to sense and act on the human environment, the IoT paradigm is both empowering and liberating.

# I.3 PURPOSE OF THIS THESIS

While other works [10, 11, 12] focused on ultra-low power hardware designs describe system-level optimizations that can be brought to the node, this thesis concentrates on the processor-level implementation and optimization techniques. Set in the IoT vision, it aims to improve the overall system power consumption of

# xviii INTRODUCTION

typical WSNs through the design and optimization of micro-controllers enabling high-level signal processing and complex power management strategies. Specifically, this thesis aims to answer the following questions;

• Can a processor provide sufficient computing performance to carry out high-level tasks and signal processing, specifically the on-board analysis of sensed image data, whilst operating within the constraints of an energy-harvesting system?

It is clear that a system running off harvested energy will have very little power at its disposal, often making it difficult to send raw data directly over the wireless link. Digital signal pre-processing and on-board decision-making can in theory considerably lower the required power, but the question remains as to whether such processing is possible under the stringent power constraints set by the power source. To determine the feasibility of such a system, an advanced 32-bit processor was designed and taped-out, employing state-of-the-art technological implementation techniques and capable of processing 32-bit data with an optional SIMD mode, in order to achieve significant energy savings over regular designs.

• Beyond traditional low-power design techniques, are there alternative circuit design strategies that could yield increased processing speed in low-power systems?

It is a well-known fact that low power can be achieved through reduction of the processing speed and capabilities. Beyond the techniques that can enable sufficient processing to achieve the previous objective, there remains the question of whether there are any alternative circuit design strategies that could achieve increased processing speed specifically in the context of low-power systems. Pseudo-synchronicity, an orthogonal circuit-level optimization technique is therefore proposed.

• How can processors be made to operate efficiently in spite of the varying workloads typical of such devices?

Much of the work required from a sensor node is data accumulation, a relatively low-power and time-insensitive task, interspersed with high-performance bursts of processing and computation, which are significantly different design targets for such systems. The question is thus whether a processor can be designed to manage both modes effectively, without undue inefficiency in either. A dual-processor system is therefore presented that is able to operate efficiently in either high-performance burst or continuous monitoring modes.

# **I.4 THESIS OUTLINE**

In order to answer the questions outlined above, the remainder of this thesis is organised as follows.

# Chapter 1

Chapter 1 presents a general introduction to the techniques used for low-power design, and the state of the art processors currently available in research. Rather than aiming towards high performance, this class of micro-controllers focuses on low power consumption in order to fit within the constraints of energy-harvesting systems. The underlying technology is presented, as well as features of the 65-nm CMOS manufacturing node used to implement later designs, along with the challenges and pit-falls that low-voltage brings. This chapter also presents the design metrics that will be used to evaluate the low-power core developed as part of this thesis.

# Chapter 2

Chapter 2 presents the work done for the design and implementation of the Bellevue processor, a custom 50MHz 32-bit micro-controller running at 0.37V built on a 65-nm LP/GP CMOS process. It features a low-power  $1.55\mu$ W sleep mode, and a variable-width SIMD pipeline and multiply/divide unit, achieving 7.7 $\mu$ W/MHz overall. The proposed micro-controller is designed to operate under the same stringent power constraints required by harvested energy operation, but with a significantly increased processing capability with respect to the state-of-the-art designs, enabling the processing of captured image data directly within the WSN. By allowing greater data processing abilities for the same low power, the WSN is able to analyse the sampled data on-chip for less energy than required for offloading to a remote node via a wireless link, thereby providing more features and better real-time reaction to events. For example, a typical image sharpening task running on-board consumes  $5.4\mu$ J and allows real-time data processing. Offloading via a wireless link would consume more, and not be able to offer the same throughput capabilities nor realtime analysis.

# Chapter 3

Chapter 3 details a circuit optimization design strategy that enables operation acceleration within a combinatorial circuit beyond that generally achievable by conventional synthesis methods, by exploiting the data-dependent delay variations inherent in such circuits. Through the automatic insertion of signal transition detectors to monitor the progress of operations underway, calculations can be prematurely completed, thereby increasing the operation speed from the worst towards the average case. In addition, a synthesis flow is proposed to increase the proportion of fast paths, thereby increasing the technique's impact. Applied automatically to a series of benchmark circuits, synthesis results show it to achieve an average performance increase of 29% over conventional synthesis, which must ensure deterministic timing closure. In spite of a 21% power overhead caused by the addition of the hardware required, this increased speed allows shorter wake periods and is thus able to lower the circuit's overall active energy by 14%.

# XX INTRODUCTION

# Chapter 4

Whereas traditional WSNs are optimized either for processing-intensive or monitoring applications, Chapter 4 presents a low-power, dual-core processor system that can function efficiently in both modes. Software running onboard can transparently switch to a workload-optimized core during execution in order to best match the application and tasks being processed. In doing so it can either provide a lower-power performance for time-indifferent tasks, and provide flexible continuous monitoring capabilities during idle periods between processing bursts, or a DSP-capable core for data intensive tasks.

## Conclusion

In the conclusion, the main contributions of this thesis are summarized, and perspectives for future research and developments are outlined.

# AUTHOR'S PUBLICATION LIST

# **Journal papers**

- JP1. D. Bol, J. De Vos, C. Hocquet, <u>F. Botman</u>, F. Durvaux, S. Boyd, D. Flandre, and J-D. Legat, "SleepWalker: A 25-MHz 0.4-V Sub-mm<sup>2</sup> 7-μW/MHz Microcontroller in 65-nm LP/GP CMOS for Low-Carbon Wireless Sensor Nodes," in *IEEE J. Solid-State Circuits*, vol. 48, no. 1, pp. 20-32, 2013.

- JP2. <u>F. Botman</u>, D. Bol, J-D. Legat, and K. Roy, "Data-Dependent Operation Speed-Up Through Automatically Inserted Signal Transition Detectors for Ultralow Voltage Logic Circuits," in *IEEE Trans. Very Large Scale Integr.* Syst., 2014.

- JP3. <u>F. Botman</u>, J-D. Legat, and D. Bol, "Ianus: a workload-optimized ULV dual-processor system for monitoring and data-processing applications in the Internet-of-Things," in *IEEE Trans. Very Large Scale Integr. Syst.*, 2014, submitted.

## Invited tutorials and keynotes

ITK1. D. Bol, J. De Vos, <u>F. Botman</u>, G. de Streel, S. Bernard, D. Flandre, and J-D. Legat, "Green SoCs for a Sustainable Internet-of-Things", in *Proc.* Workshop Faible Tension Faible Consommation (FTFC), 4 p., 2013.

# **Related conference papers**

- CP1. D. Bol, C. Hocquet, J. De Vos, F. Durvaux, <u>F. Botman</u>, D. Flandre, and J-D. Legat, "Design Techniques for Reliable Timing Closure in Ultra-Low-Voltage Logic SoCs," in *Proc. IEEE Subthreshold Microelectronics Conference*, 2011.

- CP2. C. Hocquet, <u>F. Botman</u>, D. Bol, and J-D. Legat, "A near-threshold instruction cache with zero miss overhead time for dual- Vdd microcontrollers," in *Proc. IEEE Subthreshold Microelectronics Conference*, 2011.

- CP3. <u>F. Botman</u>, D. Bol, C. Hocquet, and J-D. Legat, "Exploring the Opportunity of Operating a COTS FPGA at 0.5V," in *Proc. IEEE Subthreshold Microelectronics Conference*, 2011.

- CP4. D. Bol, J. De Vos, C. Hocquet, <u>F. Botman</u>, F. Durvaux, S. Boyd, D. Flandre, J-D. Legat, "A 25MHz 7µW/MHz ultra-low-voltage microcontroller

# xxii AUTHOR'S PUBLICATION LIST

SoC in 65nm LP/GP CMOS for low-carbon wireless sensor nodes", in *IEEE International Solid-State Circuits Conference*, pp.490-492, 2012.

- CP5. <u>F. Botman</u>, D. Bol, and J-D. Legat, "Data-dependent operation speedup through automatically-inserted signal transition detectors for ultra-low voltage logic circuits," in *Proc. IEEE Subthreshold Microelectronics Conference*, 2012.

- CP6. <u>F. Botman</u>, J. De Vos, S. Bernard, J-D. Legat, D. Bol, "Bellevue: a 50MHz Variable-Width SIMD 32bit Microcontroller at 0.37V for Processing-Intensive Wireless Sensor Nodes", in *IEEE International Symposium on Circuits and Systems*, 2014.

- CP7. D. Bol, G. de Streel, <u>F. Botman</u>, A. Kuti Lusala and N. Couniot, "A 65-nm 17-pJ/frame.pixel 0.5-V DPS CMOS Image Sensor for Ultra-Low-Power SoCs achieving 40-dB Dynamic Range," in *IEEE Symposium on VLSI Circuits*, 2014.

# "640K ought to be enough for anybody"

Widely, though incorrectly, attributed to Bill Gates, 1981.

# **CHAPTER 1**

# FUNDAMENTALS OF LOW-POWER PROCESSOR DESIGN

This chapter presents a general introduction to the techniques used for low-power circuit design, with a special focus on the stateof-the-art low-power processors. Whereas traditionally the design of a processor system is geared towards high-performance, these have energy efficiency as their primary focus, and aim to be employed in wireless sensor nodes running off harvested energy. Features of the underlying technology is presented, specifically those of the 65-nm CMOS manufacturing node which is primarily used by this work. This chapter also gives an overview of the design metrics and problems encountered when designing such low-power systems, giving an insight into the background setting of later chapters. 2 FUNDAMENTALS OF LOW-POWER PROCESSOR DESIGN

# Contents

| 1.1 | Circuit design for ultra-low power              | 3  |

|-----|-------------------------------------------------|----|

| 1.2 | ULV circuit implementation challenges           | 9  |

| 1.3 | Micro-controller design metrics                 | 13 |

| 1.4 | A brief background on energy harvesting systems | 14 |

| 1.5 | Micro-controllers for ultra-low power systems   | 15 |

| 1.6 | Next steps                                      | 18 |

|     |                                                 |    |

# Associated author publications

- JP1. D. Bol, J. De Vos, C. Hocquet, <u>F. Botman</u>, F. Durvaux, S. Boyd, D. Flandre, and J-D. Legat, "SleepWalker: A 25-MHz 0.4-V Sub-mm<sup>2</sup> 7-µW/MHz Microcontroller in 65-nm LP/GP CMOS for Low-Carbon Wireless Sensor Nodes," in *IEEE J. Solid-State Circuits*, vol. 48, no. 1, pp. 20-32, 2013.

- CP2. C. Hocquet, <u>F. Botman</u>, D. Bol, and J-D. Legat, "A near-threshold instruction cache with zero miss overhead time for dual- Vdd microcontrollers," in *Proc. IEEE Subthreshold Microelectronics Conference*, 2011.

- CP4. D. Bol, J. De Vos, C. Hocquet, <u>F. Botman</u>, F. Durvaux, S. Boyd, D. Flandre, J-D. Legat, "A 25MHz 7µW/MHz ultra-low-voltage microcontroller SoC in 65nm LP/GP CMOS for low-carbon wireless sensor nodes", in *IEEE International Solid-State Circuits Conference*, pp.490-492, 2012.

In the IoT, nodes must have powerful processors in order to provide data processing capabilities, efficiently manage the wireless network, for sensing and actuation procedures, and high-level tasks. However, the power consumption of the processor core itself is of concern.

Processors come in all shapes and forms, but as a general rule the simpler the instruction set, the lower the logic power consumption but also the longer the task will take to complete, and possible overhead from increased memory access. Although the choice of architecture is ultimately dependent on the target application, a number of design-level optimization strategies can be employed across the board.

# 1.1 CIRCUIT DESIGN FOR ULTRA-LOW POWER

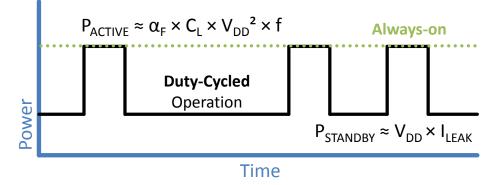

It is well known that the total power of a circuit can be modelled as  $P_{tot} = P_{leak} + P_{switch}$ .  $P_{leak}$  is the power lost through transistor leakage and factors independent of activity. The switching power  $P_{switch}$  is that which results from operation. The latter is largely due to the switching of the input capacitors of each transistor the driving gate is electrically connected to, temporary short-circuits that occur in CMOS gate designs, signal propagation along metal connections and associated capacitance and cross-talk, and other logic transition-related factors. These are proportional to the switching activity and frequency, and specifically, in the case of losses due to the input capacitors, can be modelled as  $P_{switch\_CL} = \alpha_F \times C_L \times V_{DD}^2 \times f$ , where  $\alpha_F$  is the switching activity,  $C_L$  the load capacitance,  $V_{DD}$  the supply voltage and f the operating frequency of the overall circuit.

Since in nominal conditions the switching power dominates, efforts to reduce the power consumption of a circuit will therefore attempt to minimize each component of it.

# Activity reduction

In an attempt to reduce the activity factor of circuit sections where switching is not required at certain instants, the clock can be gated [13] or data lines can be isolated through operand isolation [14] to limit redundant switching. Clock gating prevents a clock signal from activating a set of registers and cause these to switch, and operand isolation is the same principle applied to data propagation. These techniques, combined, are very effective and are widely supported by commercial design tools, which are able to automatically identify groups of cells that can benefit from gating in spite of the hardware overhead, and insert gating cells accordingly.

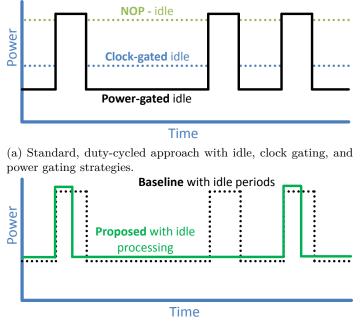

Another obvious strategy is to duty-cycle the processor and power gate it when it is no longer actively needed (see Fig. 1.1). In order to achieve this, a sleep controller peripheral can shut down the power to the processor, and control the wake cycle based on internal or external inputs. This can, for example, be combined with an RF wake-up receiver [15] to respond to wireless events, or simply wake up periodically based on a timer or on critical sensor events.

Fig. 1.1.: Typical system power consumption displaying active and standby power, and demonstrating duty-cycled operation.

# Voltage scaling

Since the switching power  $P_{switch}$  is quadratically dependent on the supply voltage, another way to lower the power significantly is to reduce the operating voltage of the circuit. In fact, the voltage can actually be reduced to below the transistor threshold voltage, where so-called sub-threshold CMOS designs have been shown to operate at down to 36mV [16]. However, this is not always a wise optimization strategy [17].

The main problem with voltage scaling is that whereas  $P_{switch} \propto V_{DD}^2$  decreases quadratically with the supply voltage, it also increases the logic delay [18, 19]. So by reducing  $V_{DD}$ , the performance achievable is also affected [20].

Similarly, although the leakage power also scales, it does so less fast thereby causing its relative contribution to become more significant at low voltage and operating frequency [21]. This results in a trade-off; on the one hand at higher voltages, high performance can be achieved at the cost of high switching-dominated energy per cycle. On the other, at low voltages, the leakage becomes increasingly dominant. Optimising for the lowest overall energy per cycle yields an energy optimal voltage (EOV) [21] at which it is best to operate, usually at ultra-low voltages (ULV).

Conversely, it is possible to look at this from a performance perspective and find for a given operating frequency the optimal supply voltage that will enable it. This is the minimum energy point (MEP) [22, 23], where for a given technology choice and operating conditions the energy per operation is at a minimum.

It is also possible to use reduced voltage swing in localised signals, as is quite frequent in SRAM memory designs. By reducing the voltage swing the resulting power consumption of the driver and sink gates will be much lower and, crucially, the required voltage level will be achieved much faster, enabling a performance increase. However, particularly in the case of ULV designs, this will further reduce the voltage margins and thus potentially degrade the stability of these signals. Overall, voltage reduction is an effective way of decreasing the power consumption of a circuit, albeit at the cost of performance. However, by combining voltage scaling to ULV with acceleration techniques it is possible to maintain performance for the targeted class of devices while achieving low power overall.

# Technology scaling

As per Gordon Moore's self-fulfilling prophecy almost 40 years ago [1], the IC device count has been increasing phenomenally through Dennard scaling [24], thereby reducing gate capacitances  $C_L$  and greatly improving the switching power at each technological node. Specifically, industry-guided scaling theory typically aims to achieve a 30% reduction in gate delay and dimensions [25, 26] at each new node.

However, because of a shorter channel and subthreshold current there results an intrinsic leakage increase, which in itself becomes an important optimization aspect [27], especially at low frequencies where leakage integrated over time becomes significant with respect to the switching power.

In order to compensate for this, it is possible to modify the underlying transistors' threshold voltage  $V_T$ , which has a localised impact on the performance and leakage of the underlying transistors. The 65-nm CMOS technology, for example, features several flavours, core oxide thickness GP and LP, and doping levels HVT, SVT and LVT<sup>1</sup>.

In a typical micro-controller context, the different underlying blocks feature differing activities, and so it is possible to differentiate their physical implementation using these flavours in order to maintain performance and minimum energy at the design point [28, 29, 30].

For example, in SleepWalker [31] there are two main activity regions. The main processor core features comparatively high activity and a clock frequency of 25MHz, so the designers chose to implement this using GP SVT MOSFETs which best fit the speed requirements at ULV (0.4V). Similarly, the peripherals and low-frequency components display much lower activity, and so are implemented using LP HVT MOSFETs at nominal 1V supply voltage. By taking advantage of technology scaling and the inherent power benefits associated with it, and combining this with a suitable choice of transistor variant and dual supply voltage, the operational requirements of the system can be well matched while maintaining a power advantage [28].

### Memories

Memories are required in a micro-controller system for storing both data and instructions, enabling the processor to perform a given function. Particularly in the case of the IoT, a large memory capacity is required for data logging, more advanced signal analysis, and complex communication stack. While external (off-

<sup>1</sup>Capabilities of the ST Microelectronics foundry, see http://cmp.imag.fr/aboutus/slides/ slides2007/04\_KT\_ST.pdf

# **6** FUNDAMENTALS OF LOW-POWER PROCESSOR DESIGN

chip) memories can be used, their access is generally very costly in terms of power, latency and system (PCB) manufacturing price.

While the research community has been intensively researching ULV SRAM memories [32, 33], some designs use foundry-optimized SRAM bit arrays in a nominal power domain in an attempt to maximize density. Their access, however, is therefore costly in terms of power due to the level-shifting necessary and the switching in the nominal power domain. However, whereas historically memories have been considerably slower than the processor itself, the voltage differential now enables both to have similar performance. An accelerating cache is therefore no longer necessary, but if implemented in the ULV region using low-power registers can be used instead to reduce the access frequency to these memory blocks and thereby save power [34]. The use of a cache in ULV designs therefore no longer serves the purpose of reducing access times, but to minimize the nominal-power domain power overhead.

SleepWalker [31, 35] takes this one step further through the design of a ULV cache that features a zero-miss delay penalty, meaning that overall memory access time from the perspective of the processor core remains the same, whether the requested data is cached or not.

The question of cache size is a design consideration, as is the choice to use memory banking, but varies significantly on a per-application basis. Dedicated simulations are needed to assess the impact of the various arrangements on the overall power consumption [36], taking into account the possible increased access time. And while having multiple memory banks may lower the access power costs through lower internal capacitances, the decoding overhead and overall increased leakage must also be considered.

Lastly, there is the question of volatility. Since non-volatile memory is typically difficult to embed into the system while maintaining a reasonable power budget, micro-controllers in wireless sensor nodes usually require their program to be given to them on activation. This can be done manually, through dedicated circuitry and an external flash memory, or through a dedicated read-only memory (ROM) that is programmed at design time. The node will then typically fetch more complete programs from the network [37].

#### Hardware acceleration

Through a careful mixture of technology scaling, voltage scaling, and transistor flavor choice, the processor is able to rapidly perform whatever operation is required of it. In fact, given the high active power, it is generally best to perform the task as fast as possible, then return to a power-gated sleep state. In this way, tasks can be duty-cycled based on usage, and the best power option obtained.

With this in mind, the advantage of having dedicated hardware to accelerate frequent tasks and return the processor to its idle state as fast as possible becomes significant. A processor may benefit from a dedicated hardware multiplier if the application requires frequent multiplications. Similarly, since cryptography will be a necessity in the IoT, a dedicated module may prove to be a necessity. Also, in applications such as biomedical devices, digital signal processing (DSP) hardware such as FFTs and FIRs can be beneficial [38]. The same is true for many other types of applications, for instance those based on machine-learning, or in baseband telecommunication systems.

As a result, the design of the micro-controller system must not only take into account features of each composing block, but also how these blocks will interact with each other in the context of the targeted application. Fundamentally, the choice of processor core and features will be gleaned from a hardware/software partitioning analysis, where potential gains can easily be identified and a balance struck between the increased power consumption, and the longer sleep time afforded to the system by its inclusion.

# Parallel execution

Although reducing the supply voltage of the processor core is an effective way of lowering the power consumption, it also negatively impacts the processing speed possible under those conditions. Technology choice can to some extent mitigate this, but in some cases this is not sufficient. Similarly, adding pipeline stages can increase throughput, but thereby also reduces the path lengths and introduces overhead from an increased number of registers.

For high-performance, desktop-class processors hitting the power density barrier, the solution was to migrate from single to multi-thread computation, and dispatching operations across multiple cores. This can also be done in ULV systems, with the added advantage that unused cores can be power gated when not in active use. In this way, and through careful design of the algorithms running on the system, tasks can be executed in parallel, and increase the effective processing speed whilst maintaining an excellent energy profile.

Similarly, whereas traditional processors sometimes implement single instruction multiple data (SIMD) instructions in order to increase performance, the same features can be used in ULV systems [39], with a view to utilize resources more efficiently and, ultimately, consume less energy by completing tasks faster.

# CPU architecture choice

There are many types of processor cores, each with their own special features and unique aspects that are useful in the context of ultra-low power systems. The MIPS architecture, for instance, has a large number of registers available for use, thereby limiting memory access, and a branch delay slot that in most implementations removes the need for a branch predictor. The SPARC architecture on the other hand uses register windows to optimize procedure calls, making interrupt handling and operating system support particularly efficient. The ARM architecture implements the Thumb instruction set, which makes a subset of operations available in reduced instruction width, thereby significantly reducing memory access costs and improving code density and thus requiring a smaller instruction memory. PIC and AVR are low-power 8-bit micro-controller families designed for simple, embedded applications requiring little processing power. And as a balance between these simple 8-bit systems and 32-bit architectures, TI's MSP430 processor claims a low-power advantage through its analog

# 8 FUNDAMENTALS OF LOW-POWER PROCESSOR DESIGN

features and fine-grained power management system. There are also some more exotic architectures [40, 41, 42, 43].

There are also attempts to automatically generate a processor instruction set that best matches an application [44]. The main advantage of processors over dedicated ASIC circuits is their flexibility, allowing changes to the software without major circuit re-design. However, such automatically-optimised instruction sets often tend to be overly specific to the target application, and therefore reduces the resulting flexibility. Also, due to the integrated nature of the instruction set in the design of the processor, such systems will either not allow many modifications, or result in a sub-optimal processor design. In many ways, therefore, fixed instruction sets have the advantage for ULV, but selecting one is a difficult choice.

As a general rule, however, the simpler a processor's instruction set, the less power the core will consume, but the greater the number of cycles required for a task to execute.

In ULV systems, the leakage is significant but can mostly be limited through power gating during sleep, so the key factors in designing ULV systems is limiting active-state switching activity and reducing overall processing time. This makes the choice of architecture highly dependent on the target application. For instance the choice of a 16-bit architecture over a 32-bit architecture is inspired. if the data to process is of that length and the memory range to access is small. On the other hand, a 32-bit or even 64-bit architecture may be necessary in order to seamlessly interface with servers and more complex control nodes in the IoT. A smaller datapath width will induce less switching when accessing the various memories, but this effect may be offset by more complex computing behind the scenes necessary to handle large numbers, or a greater number of requests. Similarly, is a 32-bit instruction set truly necessary, and does a reduced decoding complexity offset the higher instruction memory access costs? There is no definitive answer, since the application requirements are so different, but in each case the processor designer must keep these issues in mind when determining the best solution to use.

# Algorithm optimization

Although not strictly related to microprocessor optimization, the way in which it is used can have a significant impact on the overall power performance. Algorithms are implemented to efficiently implement a given task, but often with little thought about the power implications it may have on a system. For instance it may require access to both the memory blocks and a hardware accelerator simultaneously, whereas distributing these in time will have a positive impact on the peak current and, therefore, the power converter requirements and overall performance. There is thus a need to adequately study the scheduling aspects of the applications running on the system [45].

This is typically a task that is very hard to efficiently perform at the hardware level, since there is no information available at that level as to the long-term usage and actual requirements of the application. This is therefore best done at the software level, but work has been done to implement power-aware compilation [46] that will perform this analysis automatically.

Similarly, data representation should be adequately considered. On the one hand a more efficient memory storage of the data will result in fewer requests to access it, and also conserve valuable memory space. And features such as gray encoding can limit switching in the busses, which will ultimately lead to decreased active energy utilization.

### Summary

This section has briefly touched on the techniques used to decrease microcontroller power consumption, from a design perspective. Technology choice and supply voltage are crucial enabling factors, and the use of advanced nodes brings significant benefits. Execution speed is an important aspect since, combined with duty-cycling, it will allow the processor to remain inactive for longer periods and thereby achieve a power advantage. This execution speed can be improved through a variety of ways, such as hardware accelerators and operation parallelization. Memory access, and data movement more generally, can be reduced through localized caches and CPU architecture choice, but in the final analysis a system-wide power reduction can only stem from a concerted effort across all hardware blocks and co-design of the associated software.

# 1.2 ULV CIRCUIT IMPLEMENTATION CHALLENGES

Designing a circuit to function at ULV brings associated power benefits, as seen in the previous section. There remain, however, challenges from a physical implementation perspective, due to the lower voltage margins and inherent variability associated with the manufacturing process for such an advanced technology.

This section details some of the problems that are frequently encountered, and techniques used to mitigate their effects.

## PVT variation compensation

One of the main concerns are inter-die process, voltage and temperature (PVT) variations [47, 48, 49]. As part of the manufacturing procedure, there exists a process variation from die to die (D2D) that causes the underlying circuits to be implemented slightly differently. In addition, the differences in voltage and temperature where the devices will be used also causes uncertainty at design time.

In order to model these variations, chips are conventionally designed using a multi-mode, multi-corner (MMMC) analysis. The slow (SS die and low temperature at ULV) corner represents the worst-case performance the device is designed to cope with, and the fast (FF die and high temperature at ULV) corner represents the best case. In addition, some designs also consider the impacts of transistor ageing and electron-migration that affect the circuit over the long-term. Such an MMMC analysis is widely supported by the CAD tools, and

## **10** FUNDAMENTALS OF LOW-POWER PROCESSOR DESIGN

enable them to obtain not only timing closure, but also resolve setup and hold violations.

Conventionally, timing and voltage margins are inserted in order to achieve guaranteed functionality throughout the range of supported conditions. These, however, add an overhead to the system by not allowing the voltage to be lowered to the optimum, and represents wasted performance.

An alternative technique often employed is to compensate for these effects adaptively, observing the actual conditions and ensuring that the circuit operates within design specifications. One proposed approach is through the use of an adaptive voltage system (AVS) [50] that adapts the supply voltage  $V_{CC}$  to ensure appropriate performance. Such AVS units [51, 52] observe the on-chip conditions, for example through the use of a calibrated ring-oscillator (RO) in the target domain [11, 31, 51] in order to tune the voltage output optimally, with a configurable safety margin.

Conversely, this can also be done by adapting the operating frequency of the target block [53] using an adaptive frequency scaling (AFS) system. Along with AVS units, these are specific implementations of the general field of Dynamic Voltage and Frequency Scaling (DVFS) systems, which in addition to being able to adapt the operating conditions on-chip, do so adaptively according to what is actually encountered by the system during use.

The compensation condition detection mechanism could also potentially be calibrated by sensing the error rate encountered within the circuit's critical paths and ensuring optimal operation. For resolution-loss architectures [54] this can be done by determining the acceptable error rate, or, if errors cannot be tolerated, by using error-correction techniques such as Razor [55] and ensuring minimum correction delay. In this way, PVT variations can be compensated and, crucially, allows the target block to be designed for only typical (TT die at room temperature) operating conditions, thereby significantly reducing the resulting margins [31].

# Random Dopant Fluctuations

Another effect that results from the manufacturing process is random dopant fluctuations (RDF) that occur intra-die (WID). In advanced technologies, the device size is so small that it becomes particularly sensitive to the dopant chemistry, which is very difficult to control reliably. Similar effects [56, 57] include Line Edge Roughness (LER) and Line Width Roughness (LWR) [58], which result from the sub-wavelength lithography process, and wider-ranging gradient effects. As a result, in spite of designing a transistor with well-known and wellcharacterized  $V_{th}$  properties, the resulting device might suffer from unexpected deviations from the reference model. It has even been proposed [59] to exploit this as a unique and unreproducible encryption key embedded within chip.

RDFs, by their very nature, cannot easily be compensated for by the AVS systems described previously, due to their localised nature. As a result, margins must be taken, or fault-tolerant techniques must be used [55]. There also exists statistical analysis methodologies that aim to predict these effects [60] and allow

the designer to compensate for them, but these are highly resource-intensive and therefore tend to take prohibitively long to perform on a complex circuit such as a processor.

Alternatively, if the critical paths are long, their impact tends to be averaged out [61, 51, 62], which is generally the case for processor systems with reasonable pipeline depths typical of ultra-low power micro-controllers. This means that smaller margins can be used, resulting in an acceptable compromise.

# Cell library optimization

Because of the noise and variability sensitivity of devices in the subthreshold regime, standard cells designed for nominal voltage and re-characterized for ULV may perform poorly, or have yield issues. Similarly, these cells may be ideally suited to low-power operation. The construction of an appropriate cell library is thus an important aspect when designing for ULV.

The first problem is a stability issue. Because of the reduced voltage margins inherent in ULV systems, it is possible that noise or transistor variations cause signal loss through the mis-detection of a logic level. Many works have therefore produced custom cell libraries, using Monte-Carlo (MC) to simulate the impact of noise on the reliability [63, 64]. Also, although transistor stacking improves the subthreshold leakage current issue [65], it also tends to induce instability at ULV due to the reduced voltages seen by individual transistors. As a result, transistor stacking is generally limited to 3 [63, 31].

In addition, the transistor gate length can be increased (in 65-nm this would lead to an increase to ~80nm), which lowers the subthreshold leakage current, albeit at the cost of area and performance. In SleepWalker [31], this was found to only increase the area by less than 5%, but allowed the MEP to be reduced by ~15% through an improved subthreshold voltage swing and drain-induced barrier lowering (DIBL) effect reduction [66, 67].

In a similar spirit, it is also possible to re-characterise the nominal voltage foundry-provided cell library for ULV, and select only the appropriate cells, rather than having to provide a full-custom implementation of the entire library, which constitutes a considerable amount of work. It is also possible to limit the initial selection to low-driver strength cells, in order to prevent the excessive use of high-strength cells in a futile attempt to achieve stringent timing requirements during CAD synthesis [68]. Where these are specifically required, in order to drive high fan-out nets or the clock tree, they can be inserted through dedicated, supervised commands during the flow.

For this reason, the optimization of the standard cell library for the target system is often of great importance, since its misuse can easily incur manufacturing issues, yield problems, or decreased stability. Whereas custom-designed cell libraries can be designed for ULV use, careful selection of cells and recharacterisation of a nominal voltage library is also possible. There have also been attempts to replace cells in-circuit; [69, 63] used a post-layout Monte-Carlo analysis in order to detect and correct hold-time violations and determine de-

# 12 FUNDAMENTALS OF LOW-POWER PROCESSOR DESIGN

lay variability in short paths. Low-voltage cell operation is then analysed, with failing cells replaced as necessary.

# Clock tree design

A traditional clock tree (CT) at nominal voltage is implemented using a cascade of clock tree buffer and gating elements from a single root element to the leaf cells that require them. The challenges in routing the clock tree are the low-skew requirement at the endpoints, and also (because of the inherently high switching activity) the power consumption.

These challenges are even greater at ULV, since because of the variability and performance differential, the potential endpoint skew between branches of the clock tree can be significant. Typical clock trees are also relatively short, causing their variations not to be averaged out as is the case in the datapath [62].

A potential solution is to employ a common buffering stage for the entire clock tree [70]. This enables all the endpoints to be affected by the same variability, and the signal propagation issues which suffer less from this issue are easily handled by the CAD tools.

For low-power aspects, elements such as clock gating cells can be inserted to reduce unnecessary switching. In [31], these were implemented using upsized LVT MOSFETs for cells within the timing path, instead of the SVT variants employed in the rest of the logic, in order to reduce incurred delays, for a fairly modest power overhead, creating a multi- $V_T$  clock tree.

Another method would be to employ statistical timing analysis (SSTA) in order to better simulate the variability effects and plan the CT accordingly, but this is currently prohibitively computationally intensive for large designs and so is not usually possible for complex SoCs.

### Glitch reduction

Another unexpected effect of reducing the supply voltage and increased variability is the appearance of glitches [71] that are hard to model at the system-level.

Contrary to in a ring oscillator, where typically only one propagation wave exists, combinatorial blocks receive many data sources, and propagate data to a number of outputs. With added variations, signals may no longer arrive in the predicted order, thereby increasing a gate's actual activity factor  $\alpha_F$  and with it the dynamic power consumption.

While this remains a concern, requiring in the future better modelling of this effect by the design tools, designers can limit its impact through the addition of glitch-masking logic on critical nets, which charge large capacitors such as memory arrays.

### Summary

This section has briefly touched on the implementation difficulties of physically implementing ULV systems. The main issue is the unpredictable nature of transistor variability, which can induce effects that are not usually taken into consideration by traditional models. SSTA methods are able to accurately model these effects, and are progressively being integrated directly into the CAD tool flows, but remain very computationally intensive.

These effects are set to become ever more significant as the underlying technology continues to scale, and while voltage and timing margins can offer protection against them, these significantly and negatively impact the performance achievable in ULV designs. However, through the use of adaptive on-chip power converters and frequency generators, careful selection of library cells, and proper clock tree planning, these effects can be overcome for the time being without having to fall back on more aggressive circuit analysis techniques.

### 1.3 MICRO-CONTROLLER DESIGN METRICS

In order to achieve this thesis' goal of optimizing a micro-controller for low-power operation, it is important to define metrics in order to evaluate the impact of the various techniques employed. In general, there are two distinct aspects of processors that need optimizing in the context of WSNs; the power, and the speed.

The power aspect is fairly straightforward, in that since the useful payload of a WSN is the sensor and data transmission to a control node, the microcontroller must strive to contribute as little power as possible and even attempt to reduce the overall system power consumption through data processing techniques. This translates to minimizing  $P_{tot}$ , the total power consumption of the micro-controller system.

It is also necessary to consider the speed at which an operation is able to execute. For this, the latency and throughput of the processor system will be considered, and thus also the operating frequency, which all have to be maximized.

Since one of the optimization techniques outlined in Section 1.1 requires good duty-cycled performance, another criteria is the inactive power  $P_{sleep}$  consumed by the processor when it is inactive. Ideally, this should be as close to zero as possible, since this represents wasted power. Similarly, it is necessary to consider the sleep and wake times, the delay required in order to transition to and from sleep and active states. This phase is problematic from a power consumption viewpoint, since whereas the processor is still not achieving productive operation, it is generally ramping up its power consumption. These times therefore also need to be optimized.

A standard micro-controller power metric is the power consumed normalized to the frequency of operation, expressed in micro-Watts per mega-Hertz ( $\mu$ W/MHz). This is equivalent to the power per instruction and power per operation. Assuming processor systems have comparable latencies and code lengths required to implement a specific task, this metric allows the comparison between different systems and optimization techniques. However this alone is insufficient in this case, since this would favour a system that consumes nothing but does not necessarily do much either. What the system is capable of doing during each

### 14 FUNDAMENTALS OF LOW-POWER PROCESSOR DESIGN

cycle must therefore be considered, as well as the time required to perform a given task. The former is given by a list of features of the instruction set, while the latter is given by the operating frequency.

One unbiased metric for gaining an insight into the performance of a processor is simply the energy required to perform a given task,  $E_{task}$ . Minimising this will ensure that the average performance of the system is adequate, but also that it can efficiently execute tasks requested of it by the application and minimise the time required to do so. This will allow features such as parallel data processing, which consume more per operation but allow the much faster execution of a task. One danger with such a metric is a tendency to over-optimise for a given task, which is why all features of the processor are discussed from the viewpoint of a common need for these types of applications in the context of the IoT, and the benchmark programs chosen are representative of tasks that could actually be encountered in real-life applications.

The optimization objective of this thesis is, therefore, to reduce the energy per task of the resulting system, under the constraints of 10-100MHz operation and with an average energy within the capabilities of the power management system. The further objective is to ensure that the resulting system is more effective than the raw transmission of data with offline processing, to achieve the same end result.

### 1.4 A BRIEF BACKGROUND ON ENERGY HARVESTING SYSTEMS

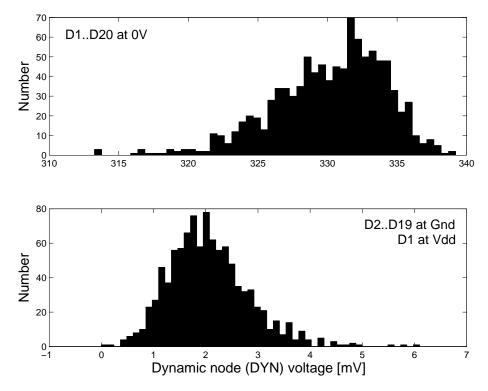

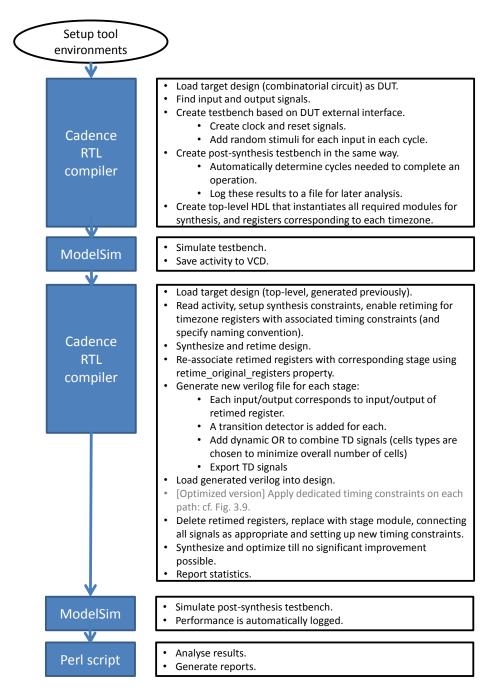

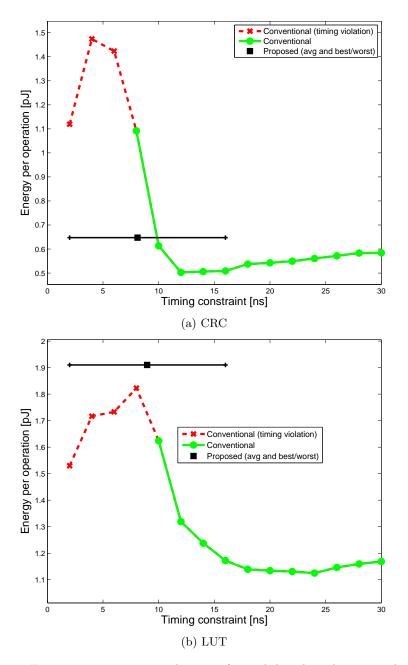

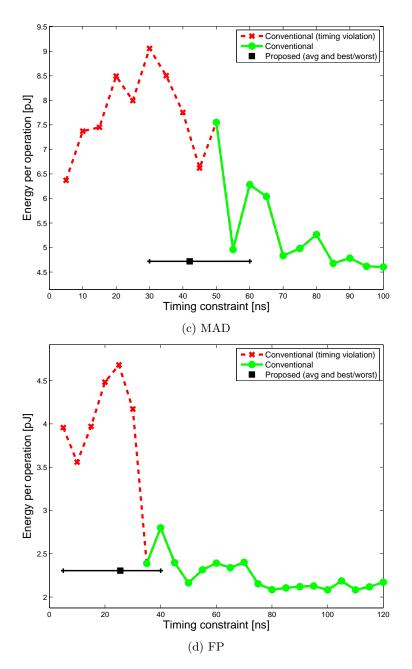

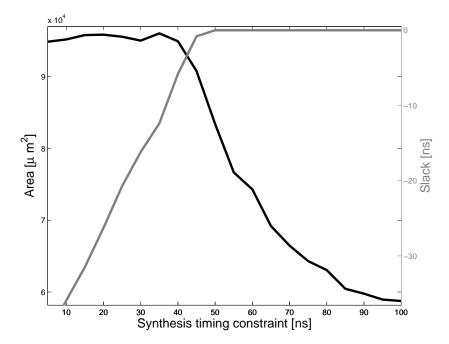

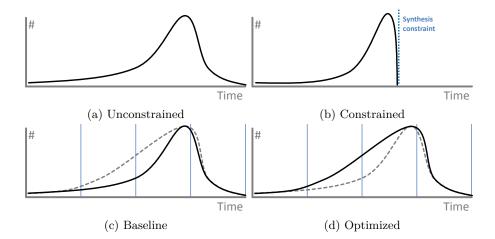

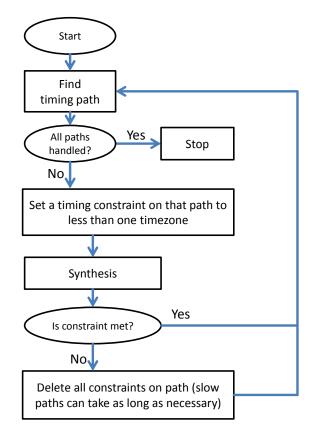

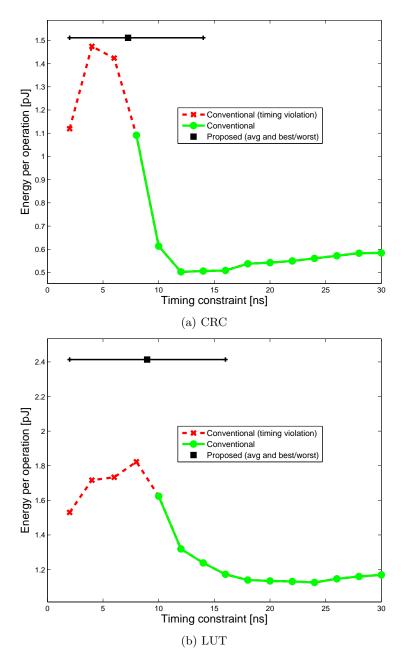

Since the aim of this thesis is to design a processor system capable of operating on harvested energy, it is necessary to briefly present the different options available. The aim of an energy harvesting, or energy scavenging, system is to obtain power for the node through ambient means, so that the device does not have to be powered externally and can thus, in theory, operate continuously for the duration of the device lifetime. This means energy harvesting seeks to capture wasted ambient power and put it to good use.